Hvordan lage en Pulse Width Modulation (PWM) i en Verilog modul kjører du en Motor / Servo

En pulsbreddemodulering er en måte å kontrollere rotasjon eller posisjonen av en elektrisk motor eller servo.

Ved hjelp Verilog HDL, vil jeg vise hvor enkelt det er å bruke tellere for å skape en PWM.

Bruksanvisning

1 Så hvordan en PWM arbeid?

Å ha en periodisk firkantsignal, endrer vi driftssyklus (modulerer) for å være mindre eller større, og derfor kontrollere vår enhet.

Hvorfor bruke en PWM?

Det er en enkel digital-til-analog konvertering teknikk som ikke krever en ADC.

2

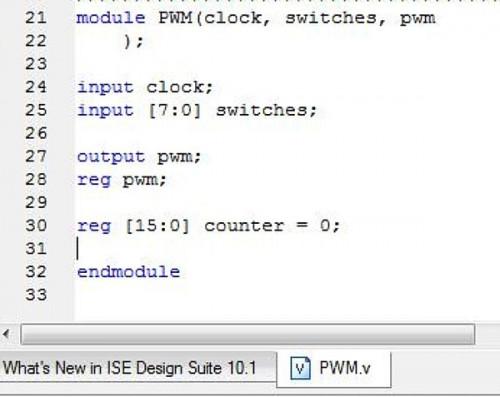

OK, så kan tenke hva innganger, utganger, registre og tellere vil vi trenger og hvilken design vi ønsker å skape.

Jeg vil bruke de åtte brytere på Spartan FPGA bord for å kontrollere hvordan mine motor / servo beveger seg eller hvor fort eller sakte jeg vil den skal bevege seg.

Innganger: klokke, 8 brytere

Utganger: PWM

Registre: PWM

Tellere: 16 bit teller (vil forklare hvorfor 16 bit senere)

3

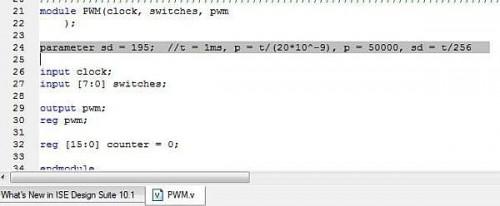

Vite hva som er klokkehastighet på FPGA og hvilken periode du ønsker å bruke.

Jeg har en Spartan FPGA bord med en 50MHz klokke. Jeg ønsker å oppdatere signal hver 1 millisekund (t). Vi bruker følgende beregning for å finne bølgeformen perioden (p)

p = t * FPGA clock

I mitt tilfelle:

p = .001 seconds * 50MHz = 50000

Å vite min p er viktig for å beregne min trinn forsinkelse (sd):

sd = p / 256 = 195

Hvorfor gjorde jeg bruke 256? Jeg skal bruke 8 brytere for å styre min servo / motor, så 2 ^ 8 = 256.

4

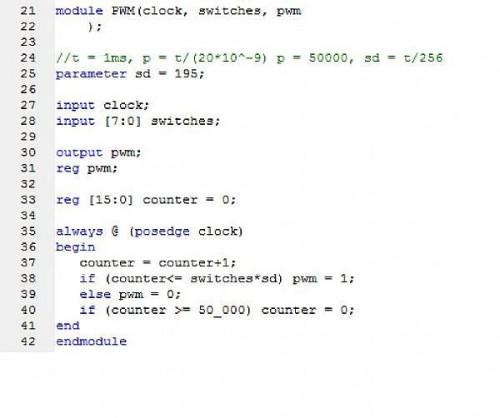

Til slutt ønsker vi å bruke vår telleren som vår plikt syklus. For å beregne hvor mange biter komponere vår teller vi bruke:

log2 (sd) = hvor mange biter er vår teller

Mens telleren er mindre enn sd (trinn forsinkelse) multiplisert med brytere verdi (som kan variere fra 0 til 255), dette er vår plikt syklus.

Hint

- Når du oppretter registeret disken må du ha det initialisert til null ellers programmet vil ikke fungere.